定制热线:0755-22277778

电话:0755-22277778

手机:13826586185(段先生)

传真:0755-22277776

邮箱:duanlian@xianjinyuan.cn

1.引言

独学而无友,则孤陋而寡闻;

2.背景介绍

某控制器产品在做屏蔽材料 www.leird.cn认证测试中,ESD±6KV接触放电出现通讯故障死机问题,需要重启后可恢复,针对此问题进行分析和整改。

3.分析与整改

3.1控制器组网与实验点

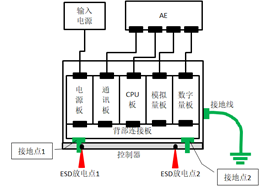

控制器组网与ESD放电点示意图参见图1所示。

(a)组网与放电点示意图

(b)放电点实物图

图1控制器组网及实验点

3.2试验现象

ESD接触放电±6KV,对放电点1和放电点2进行试验时(每个点放电3-6次左右),及放电点3(每个点放电10-20次左右)就会出现通讯故障,无法与上位机通讯,处于死机状态,需要重动恢复。放电点4试验无问题。

3.3接地可靠性排查

3.3.1接地点阻抗测定

利用万用表对盖板接地点阻抗测定,结果如下:

表1接地阻抗

|

盖板接地点 |

接地阻抗 |

备注 |

|

接地点1 |

0.2-0.3Ω |

接地阻抗较大,接地效果不好 |

|

接地点2 |

0.2-0.3Ω |

|

|

接地点3 |

0.1-0.2Ω |

接地阻抗大,接地效果不佳 |

|

接地点4 |

0-0.1Ω |

一般可接受 |

注:ESD频谱达到GHz频段,利用万用表进行机壳接地阻抗值是不准确的,但可以做为初步的定性分析判断。

3.3.2机壳接地点变更排查

对控制器的接地点位置进行人为变更,对各放电点进行ESD实验,验证各接地的可靠性,详细结果参见表2。

表2机壳接地点变更实验结果

|

盖板放电点 |

实验结果 |

|

|

初始实验接地配置 |

放电点1 |

Fail |

|

放电点2 |

Fail |

|

|

放电点3 |

Fail |

|

|

放电点4 |

Pass |

|

|

接地点变更:靠近接地点2 |

放电点1 |

Fail |

|

放电点2 |

Pass |

|

|

放电点3 |

Pass |

|

|

放电点4 |

Pass |

|

|

接地点变更:靠近接地点1 |

放电点1 |

Pass |

|

放电点2 |

Fail |

|

|

放电点3 |

Fail |

|

|

放电点4 |

Pass |

|

3.3.3接地可靠性排查小结

(1)接地点位置变更后到2后,放电点2/3/4实验没有问题,但放电点1仍然会导致通讯故障死机;接地点位置变更后到1后,放电点1/4实验没有问题,但放电点2/3仍然会导致通讯故障死机。

(2)盖板与机壳地搭接不良,接地点1/2/3接地阻抗较大,接地点4的阻抗可接受;

(3)整体的控制器盖板与机壳的搭接设计不可靠,导致ESD测试中会出现问题。

3.4接地不良导致通讯故障死机问题分析

3.4.1ESD耦合机理分析

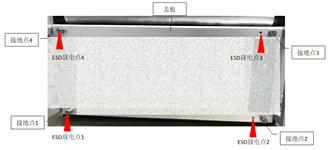

3.4.1.1ESD波形参数

IEC61000-4-2标准中ESD放电电流波形参数如图2所示[1],6KV的放电电流峰值为22.5(1±15%)A。

图2接触放电电流波形参数

3.4.1.2ESD频谱特性

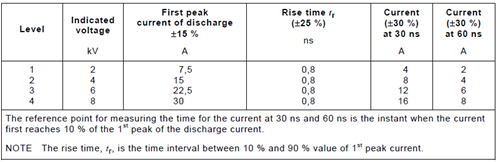

6KV等级ESD的放电电流与频谱特性参见图3和图4所示[2]。ESD的幅值一般在频率0~1.2 GHz间,超过1.2 GHz幅值基本衰减为0,整个频率期间出现了2次峰值.频率在0~30 MHz间,幅值逐渐衰减,并且衰减较快.然后随频率增加至60 MHz时,幅值达到第二个峰值,随着频率继续增加,幅值逐渐衰减至0。

图3 6KV放电电流波形

图4 6KV接触放电电流频谱

3.4.1.3ESD放电耦合机理分析

(1)ESD的干扰模式

ESD以共模干扰方式对控制器进行干扰,主要有以下几种形式:

◆ESD放电中形成的场耦合,一般发生在接地点良好,但接地位置附近有敏感信号或走线的情况:

◆ESD放电电流在接地阻抗路径中形成噪声电压Vnoise干扰敏感设备,一般发生在接地不良,接地阻抗较大的情况;

◆ESD放电电流直接注入敏感信号中,一般发生在对pin进行ESD注入实验的情况。

(2)结构地分析:

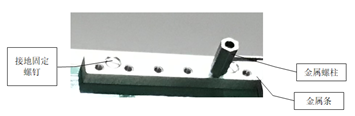

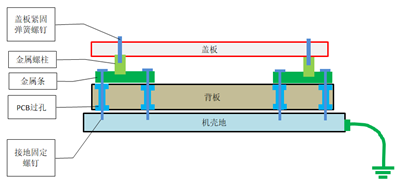

控制器盖板接地的结构层次:盖板紧固弹簧螺钉→金属螺柱→金属条→接地固定螺钉→机壳地。PCB过孔无接地铜盘,与金属条和机壳均无搭接。金属条与机壳的搭接仅仅通过螺纹进行,搭接不可靠,阻抗大,结构接地详见图5所示。

(a)盖板接地点实物图

(b)盖板接地结构示意图

图5盖板接地结构

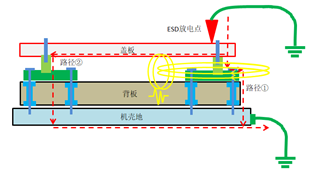

(3)干扰路径与等效机理电路分析

◆当盖板与机壳地间的接地良好时,阻抗足够低,与机壳形成等电位搭接,无压差。

ESD的主要放电路径为图6中的①和②,因①的接地物理路径较近,大部分干扰会从①路径中流到大地。流过路径①附近的电流形成的干扰场,会串扰周围的敏感信号或敏感走线。

图6 ESD放电路径示意图

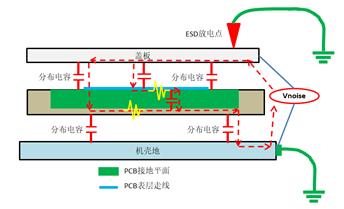

◆当盖板与机壳地间的接地搭接较差时(搭接阻抗较大),ESD放电电流会在搭接点处形成噪声电压Vnoise。

噪声电压通过盖板与PCB板件的分布电容,形成干扰电流流过PCB,使得敏感干信号受干扰,参见图7所示。

图7接地不良的ESD耦合机理示意图

先进院(深圳)科技有限公司, © 2021 www.leird.cn. All rights reserved 粤ICP备2021051947号-1 © 2021 www.xianjinyuan.cn. All rights reserved 粤ICP备2021051947号-2 网站地图